Network Stomper開発 Project 基板設計記[第3回(全5回)]

2019年11月13日 水曜日

![「Network Stomper開発 Project 基板設計記[第3回(全5回)]」のイメージ](https://eng-blog.iij.ad.jp/wp-content/uploads/2019/10/6bae6845cb53172d02351d066186c023.png)

CONTENTS

IIJは今年8月3日、4日に開催されたDIYのイベントMaker Faire Tokyo 2019に出展しました。展示テーマの一つ「音楽×IoT」の作品として、IPネットワーク経由でギターのエフェクタを操作する「Network Stomper(ネットワークストンパー)」を制作し、会場でギターの実演を行いました。

エフェクターを遠隔操作「ネットワーク・ストンパー」(Maker Faire Tokyo 2019)

このNetwork Stomperのコアになるハードウェア(制御ボード)は、IIJのエンジニアが一から開発しています。ハードウェアの開発は電源やノイズなど、ソフトウェアやネットワークの開発と異なるポイントに気をつけなければなりません。

実際に開発を担当したIIJ技術研究所の末永が、ハードウェア設計についてのレポートをまとめましたので、5回に分けて掲載します。

- 第1回 設計方針とESP-WROOM-02

- 第2回 電源回路

- 第3回 入出力回路(本記事)

- 第4回 USBシリアルインターフェース

- 第5回 製造

(編集部)

スイッチ入力回路

全体像

スイッチ入力回路は3系統あり、各回路の構成はまったく同じです。目的はESP-WROOM-02のI/Oピンの電圧を切り替えてdigitalRead()でスイッチの状態を読み取れるようにすることです。

I/OピンとしてはIO13,15,16を利用しています。このうち、IO15はブートモードの選択に利用され、起動時はLOWレベルになっている必要があります。本来は回路にリセットがかかる際にはIO15を切り離してLOWレベルに固定するようなリセット回路を設計しなければいけないところですが、今回は省略します。スイッチを押すのは人間ですので、注意書きでカバーです。外付けのスイッチ回路をつなげる場合は問題になるかもしれません。

スイッチというと気になるのはチャタリングです。ポーリングではあまり問題になりませんが、割り込み駆動にした場合には割り込みが多発してソフトウェア的なフィルタリングが必要になりちょっと面倒です。常套手段としてはコンデンサを使ったLPFを付けておくことになります。

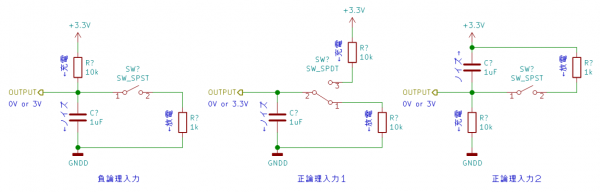

正統的な設計としては、スイッチOFF時にコンデンサを充電しておいて、スイッチがONになると放電されるという負論理入力回路が考えられます。スイッチをSPDTタイプにすると、正論理入力を作ることもできます(正論理入力1)。また、コンデンサを電源側にもってくるとSPSTスイッチで正論理入力を作れます(正論理入力2)。

ソフトウェア的には正論理にしておいたほうがわずかながら分かりやすくなります。しかし、スイッチをSPDTにすると(正論理入力1)ピンヘッダ経由で外付けスイッチを使うケースで配線が増えて不便です。SPSTで正論理を作ろうと思うと(正論理入力2)、ノイズが電源側に流れたり、逆に流れてきたりという問題が生じます。また、GPIOを出力に設定してLOWからHIGHに遷移させると、正論理入力2の回路はコンデンサにたまっている3.3Vの低位側電位を持ち上げて電源ラインを6V前後に昇圧させてしまいます。LDOががんばって抑え込むはずですが、あまり気持ちよくはありません。ダイオードと組み合わせればGPIOで高圧パルスを作る回路として使える可能性はあり昇圧回路の実験としては面白いですが、今回の用途には不適と言えるでしょう。というわけで、素直に負論理入力にしました。

回路図

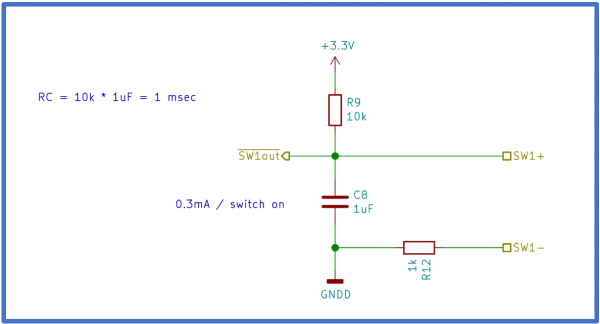

下図に回路図の拡大を示します。3系統同じものがならんでいますので、1系統分を抜粋しています。

スイッチは負論理入力とし、充電側(R9,R10,R11)に10kΩ、放電側(R12,R13,R14)に1kΩとしました。スイッチがONになっていると、抵抗が直列に繋がれて10:1に分圧されるため、GPIOには0.3Vが入力されます。コンデンサ(C8,C9,C10)はスイッチOFFで3.3Vに充電されており、スイッチONで0.3Vまで放電されます。コンデンサの容量次第でLPFの効きが変わってきますが、現在は1uFで設計しています。スイッチONで0.1msec、スイッチOFFで1msecの動作遅延となります。

観測してみると基板上のタクトスイッチだとチャタリングはあまり目立たないのですが、外付けのスイッチなどで試してみると0.4msecから0.5msec程度の期間発生することがあり、パルス幅が80usec以下という感触です。完全ではないにせよ、ある程度は抑え込めるのではないかと思います。

波形

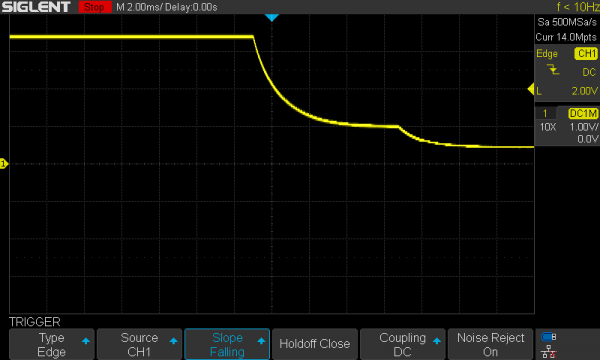

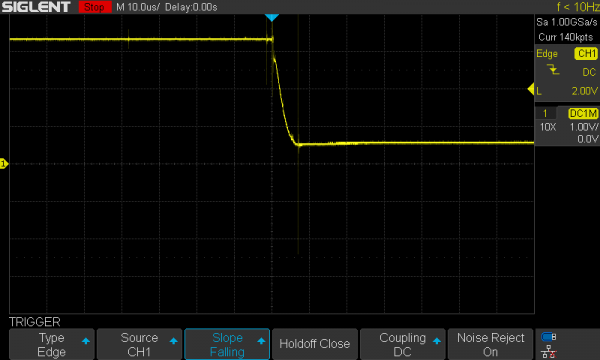

上図は基板上に実装したタクトスイッチを押した際のIO13への入力波形です。自然な放電曲線になっており、これならチャタリングの問題は生じないと考えられます。

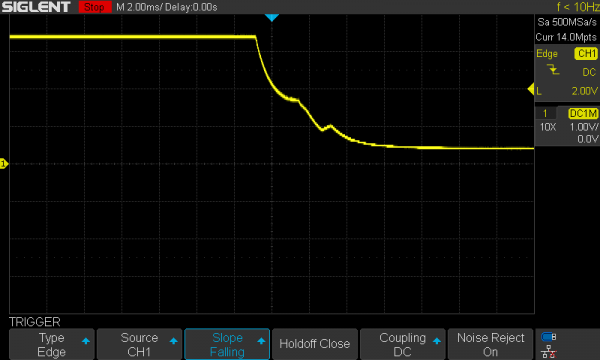

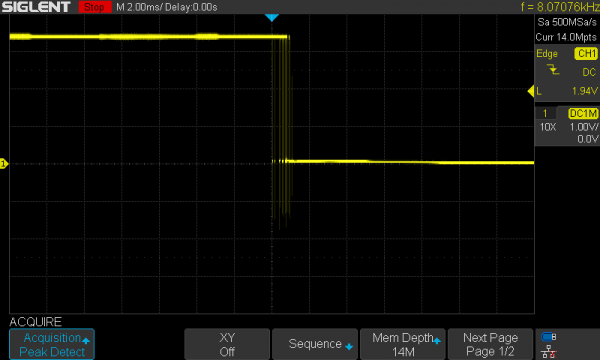

上図はピンヘッダにワニ口クリップを噛ませて外部のスイッチを押した場合の波形です。波形に段差が付いている部分がスイッチの物理的な接触状態の兼ね合いで抵抗値が綺麗に下がらなかった箇所だと思われます。比較的悪い測定結果を拾いました。

上図はピンヘッダにワニ口クリップを噛ませて外部のスイッチを押したケースでもっとも悪い結果となったものです。ひどい回路を作って、中途半端な押し方をするなど、がんばらないとこのような波形は取れませんが、スイッチの付け方次第では電圧が一旦上昇してしまうケースはまだ残っていることがわかります。R9やC8を大きくして遅延を伸ばせばもう少し軽減できるかもしれません。

上図はC8ではなく、GNDにスイッチを直結した場合の波形です。横軸が2msではなく10usになっている点に注意してください。コンデンサがないので急峻な変化をしています。画面中央付近で上下に線が滲んで見えるところがチャタリングで電圧が急激に上下しています。以前のC8経由の波形と比較すると、チャタリング防止回路により電圧の急激な変動が綺麗に取り除けていることがわかります。実験に利用したスイッチは単体でも比較的優秀で、チャタリング防止はなくても動きそうでした。

基板上には低性能スイッチの代表格である機械式リレーが載っていますので、これの波形をみてみます。機械式リレーは磁石でバネに繋がれた接点を引きつけるという構造ですので、接点のバウンドが生じやすくなっています。波形からも少しバウンド感を感じられるのではないでしょうか。

横軸は2msです。1ms程度の期間激しく電圧が上下しているのがわかります。リレーY14H-1C-5DSの仕様では動作時間は5msとありますので仕様に対しては十分に余裕のある波形です。ときどき電圧が負まで下がるのはリレー内部のインダクタンス成分(コイル)の効果でしょう。電圧が下がった後もコイルの生み出す電流が流れ続けるため、過剰な電圧降下が発生するものと考えられます。これだけ激しく電圧が上下すると、割り込みが複数回生じる可能性は高くなります。

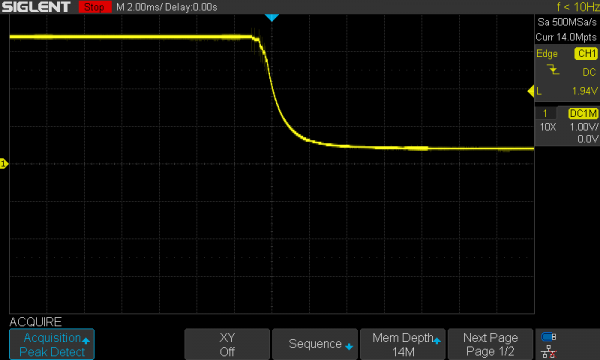

これをチャタリング防止回路に接続した場合の波形は以下のようになりました。

横軸は同じく2msです。よ〜くみるとリレーが動作を開始したタイミングでは電圧が揺れていますが、振幅はかなり抑えられていることがわかります。2Vを下回るようにはみえませんから、誤検知の心配はほぼないでしょう。電圧が1Vを下回って、GPIOがLOWを検知するころにはリレーの動作はすっかり落ち着いており、綺麗な放電波形になっています。これであれば、リレーを使って複数の基板を連動させることもできそうです。あえて機械式のリレーで通信するような使い道は思いつきませんが、通信を音で感じ取れるという構造はMaker Faire的にはアリかもしれませんね。40年くらい前の電話の交換局のような心地よいリレーサウンドを聞けるかもしれません。通信速度は100bps程度ですけど、温度センサの値を読むくらいなら問題ないでしょう。

リレー出力回路

概要

リレー出力回路は電気的な接続を避けつつ、外部の機器をON/OFFするための回路です。リレーとして利用できる素子としては、機械的なスイッチを電磁石で操作する機械式リレーと、半導体のON/OFFを光信号などで操作する半導体リレー(SSR)が存在します。

性能的には概ねSSRが優れており、消費電力に関してもノイズに関しても動作速度に関しても寿命に関してもSSRを選んでおいたほうが高品質な回路を作れます。秋葉原で買える汎用SSRとしてはパナソニック電工のPhotoMOSリレーAQYシリーズなどがあります。SSRにはDC専用やAC専用という品種も多いので、ここは注意しておく必要があります。

一方の機械式リレーは性能には見るべきものは特にありませんが、出力側のシンプルさが魅力です。単なる機械式のスイッチですから。また、動作するときにカチカチ音がなるのも魅力です。人によりますが。入力側に関しては磁気回路ということもあって必ずしもシンプルとは言えません。

説得力は特にありませんが、今回はカチカチ音を評価して機械式リレーを使いました。設計のポイントとしては、電磁石が十分な力を発揮するためにはそこそこ電流を流す必要がある、電源供給を止めると電磁石は発電機として機能する、出力側はチャタリングが激しい、などの問題への対処が挙げられます。今回の負荷はソレノイドですのでチャタリングは気にしませんが、入力側については気を使う必要があります。

回路図

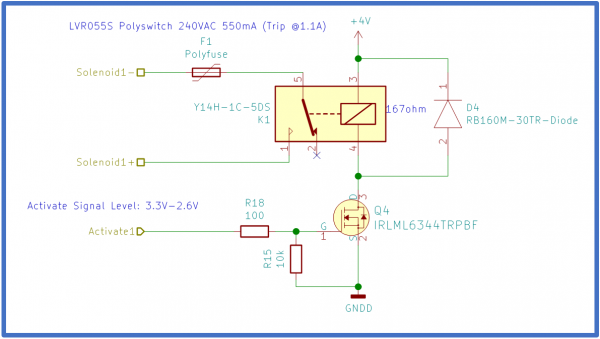

リレー制御回路は同じものが3系統載っていますので、一つを拡大します。

GPIOの出力はActivate1に入ってきます。この信号はQ4(IRLML6344TRPF, Nch MOSFET)のゲートに接続されています。Q4はリレーのコイル電流をグランド側でON/OFFするローサイドスイッチとして利用しています。スレッショルド電圧Vgs(th)は最大で1.1Vですから、Activate1がHIGH(約3V)を出力すると確実にONにできます。Vgsが3VだとON抵抗Rdsは完全には下がりきらないのですが、データシートをみると40mΩ以下にはなりそうです。今回はリレーK1(Y14H-1C-5DS, 5V機械式リレー)の制御用コイルが167Ωの抵抗を内蔵していますのでQ4のRdsは誤差の範囲といえます。

リレーの出力側に入っているヒューズF1(LVR055S, Polyswitch)は電流制限用のヒューズです。高分子ポリマーに導電性の粉末を混ぜたポリヒューズという部品で、作動してOFFになったとしても負荷をはずしておけば自然と元に戻るという性質があります。原理としては電流が大きくなって温度があがるとポリマーが膨張して粉末の密度が下がり電流が流れにくくなるというものです。今回は1.1A流れると制限がかかる部品を採用しました。一旦制限がかかると電流が550mAを切るまでは制限がかかり続けます。リレーK1の定格が最大1Aで、そこまではぎりぎり耐えますが、1Aを10%程度超えたところで強制的に電流が遮断される仕組みです。基板としては安定して利用できるのは500mAまでという仕様にしてシルク印刷を施してあります。

R18はQ4のゲートのスイッチング速度を制限し、高周波ノイズの定在波を減衰させるためのゲート抵抗です。今回は定番の値として100Ωを使っています。K1のスイッチング速度が5msですので、Q4のスイッチング速度が問題になることはありません。

R15はQ4のゲートに溜まった電荷をグランドに捨てるための抵抗でこちらも定番の10kΩを利用しています。この回路ではActivate1がGPIOの出力になりますので、通常はGPIOがLOWを出力しているのであれば電荷はGPIO側に吸われていきます。しかし、再起動などでGPIOがハイインピーダンス状態になっている間は電荷の行き場がなくなってしまいますのでR15で確実にグランドに落としてQ4の動作を安定させるようにしています。

R15にはもう一つ、ESP-WROOM-02のGPIOのpull downという役割もあります。特に重要なのはIO15に接続されているActivate3です。IO15はブートセレクタとして使われるピンの一つで、起動時にはLOWにしておく必要があります。

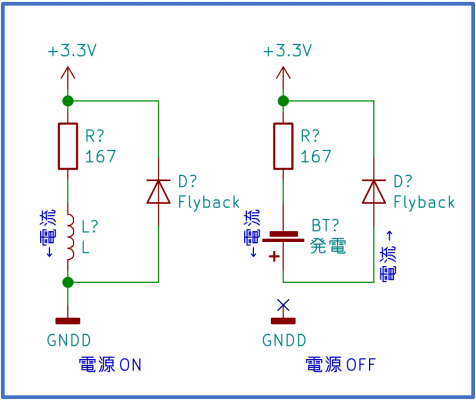

D4(RB160M-30TR, ショットキーバリアダイオード)は、K1のコイルへの電源供給を停止した際に働くダイオードです。下図にK1のコイル部分の動きを示します。

Q4がONの場合、コイルLには電流が流れ磁界が発生します。これによりリレーが動作します。Q4をOFFにするとコイルLには電流が流れなくなります。このときL周辺の磁界も減少していきますが、これによりLは発電機として動作して電流を維持(磁界の減少に抵抗)するように働きます。ここで電流を流してあげないと、発電機の出力を開放にしている状態となり理論上無限に電圧が上昇してしまいます。機械式のスイッチであればまだしも、今回の回路では、この電圧がQ4のドレインにかかることになり、故障やノイズの原因となります。ここで活躍するのがD4で、コイルの両端をつないで電流を流すことで磁界のエネルギーを消費し、過電圧を防いでいます。このダイオードの呼び方は定まっていないようで、フライホイール・ダイオード、フリーホイール・ダイオード、フライバック・ダイオードという表記をよく見かけます。文脈により使い分けるべきなのかもしれませんが、よくわかりません。電源回路に関してはフライバック電圧とフライバック・ダイオードという使い方が多いようです。

波形

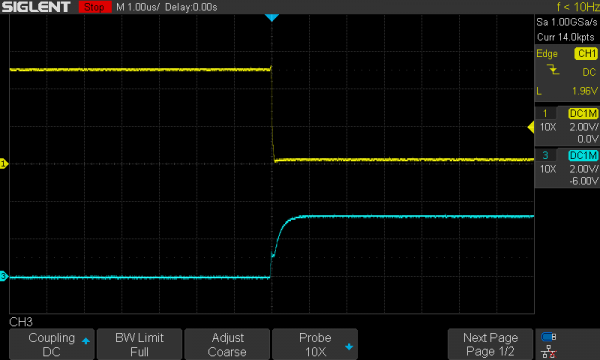

上図のチャンネル1(黄色)はQ4のドレインの電圧を観測した波形です。横軸は1usで短時間の波形をみています。縦軸は2Vになっています。リレーは5V系の電源で動作していますので電圧は高めです。電源電圧は4.5V前後となっていますが、これは5Vの電源系に逆流防止用のダイオードが入っており、その分だけ5Vから電圧降下しているためです。FETはグランド側(ローサイド)のスイッチとなっていますので、4.5Vであればリレーに電流は流れず、0Vに落ちるとリレーに電流が流れるという動作をします。

チャンネル3(水色)は同じくQ4のゲート電圧をみています。Q4の入力容量によりコンデンサの充電波形になっていることがわかります。ただし、Q4のデータシート上の入力容量は650pFに対してオシロスコープのプローブの容量は16pFですので、測定環境の影響を無視できません。参考程度と考えてください。ゲート側の電圧に変曲点があるのは、FETがONになりドレイン側の電圧が降下することで、FETの入力容量の一つであるゲート-ドレイン間容量の充電状態が変化するためではないかと思います。とはいえ、測定環境の影響も考えられ、はっきりとしたことはわかりません。ドレイン側はONのタイミングでわずかにオーバーシュート、アンダーシュートが見えますが問題になる大きさではなさそうです。

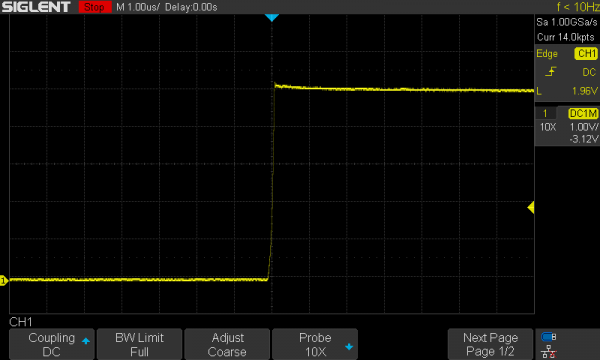

上図は逆にリレーをOFFにする際のドレイン電圧を観測した波形です。縦軸を拡大しています。大きなフライバック電圧は見当たりませんので、リレーのON/OFFを繰り返してもFETにダメージが入ることはなさそうです。

(第4回に続く…)

引用文献

- Espressif Inc. (2015年8月1日). ESP8266EX Datasheet v4.4.

- Espressif Inc. (2016年1月). ESP8266 System Description v1.4.

- Espressif Inc. (2017年5月). ESP8266 Technical Reference v1.3.

- Espressif Inc. (2018年3月). ESP-WROOM-02 Datasheet v2.6. 21.

- Espressif Inc. (2018年12月). ESP8266 Hardware Degisn Guidelines v2.4.

- Espressif Inc. (2018年12月13日). ESP8266 Pin List.

- Espressif Inc. (2018年11月). ESP8266EX Datasheet v6.0.

- Phillips Semiconductors. (2000年1月). I2Cバス仕様書 v2.1.

- Pull up resistors. (2015年9月9日). 参照先: ESP8266 Developer Zone: https://bbs.espressif.com/viewtopic.php?t=1079#p4097